对此,台积电2nm产能建置估计将进一步扩大,竹科宝山可盖四期、高雄二期,此外还有南科厂区相关规划若成真,估将有助于台积电2nm家族冲刺达至少八期八个厂的产能。

钛媒体App 4月4日消息,对于地震所造成影响,台积电方面表示,虽然部分厂区的少数设备受损并影响部分产线生产,主要机台包含所有极紫外(EUV)光刻设备皆无受损。“在地震发生后10小时内,晶圆厂设备的复原率已超过70%,新建的晶圆厂(如晶圆十八厂)的复原率更已超过80%。台积电目前正与客户保持密切沟通,将继续密切监控并适时与客户直接沟通相关影响。”台积电说。但仍有消息称,此次地震对台积电第二季财季的影响约6000万美元,对此,台积电表示,该消息“非台积电发布”。 (第一财经)

IT之家 6 月 19 日消息,消息源 DigiTimes 表示台积电已经开始在其 3nm EUV FinFET 代工节点上,为英特尔量产 Lunar Lake 和 Arrow Lake 的组件(Tile)芯粒。

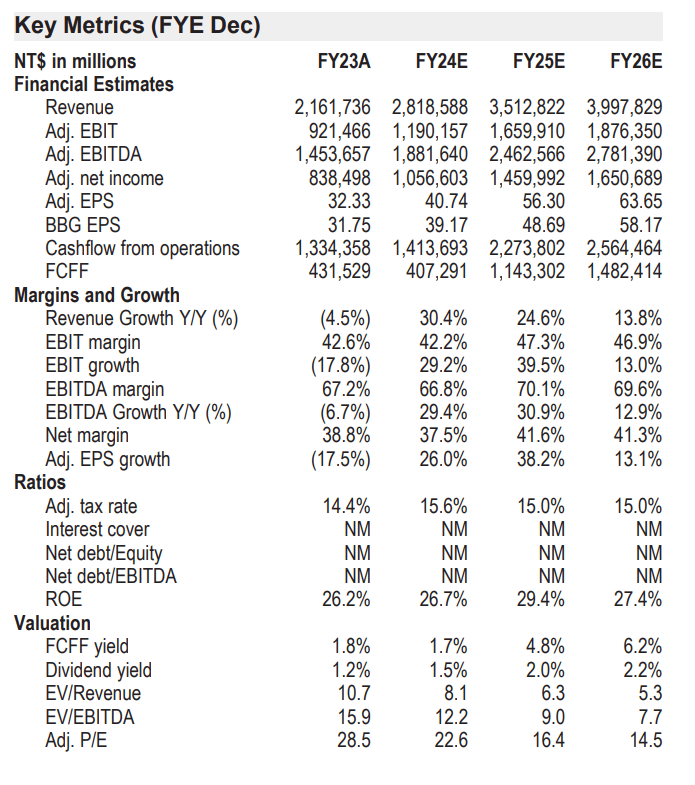

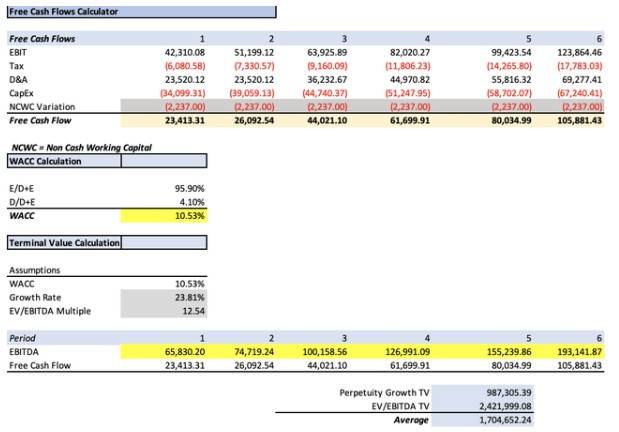

财务数据显示,截至2024年03月31日,台积电收入总额5926.44亿台币,同比增长16.52%;归母净利润2254.85亿台币,同比增长8.94%。

在芯片制造中,芯片封装技术曾被认为技术含量较低,但它在保持半导体进步速度方面变得越来越重要,对于像英伟达 H200 或B200 这样的 AI 计算芯片,仅仅使用最先进的芯片生产技术是不够的。

“摩尔定律”放缓后,台积电也在持续突破。近日,台积电资深副总经理暨副共同首席运营官张晓强在2024技术论坛上宣布,台积电已经在实验室做出CFET(互补式场效应晶体管),并计划将CFET导入下一代先进逻辑工艺中。三星、英特尔这两家芯片巨头也在积极开发CFET。

全球领先的半导体制造巨头台积电刚刚对外正式公布了其2024年6月份的财务业绩。

三星电子半导体(DS)部门前负责人 Kyung Kye-hyun 于今年 3 月出席股东大会,详细阐述了推行 PLP 技术的必要性。

PLP封装是一种将晶粒重新排列在更大的矩形面板上的封装方案(见下图左侧)。